资源详细信息

FPGA片内FIFO读写测试Verilog逻辑源码Quartus工程文件+文档说明 使用 FPGA - 资源详细说明

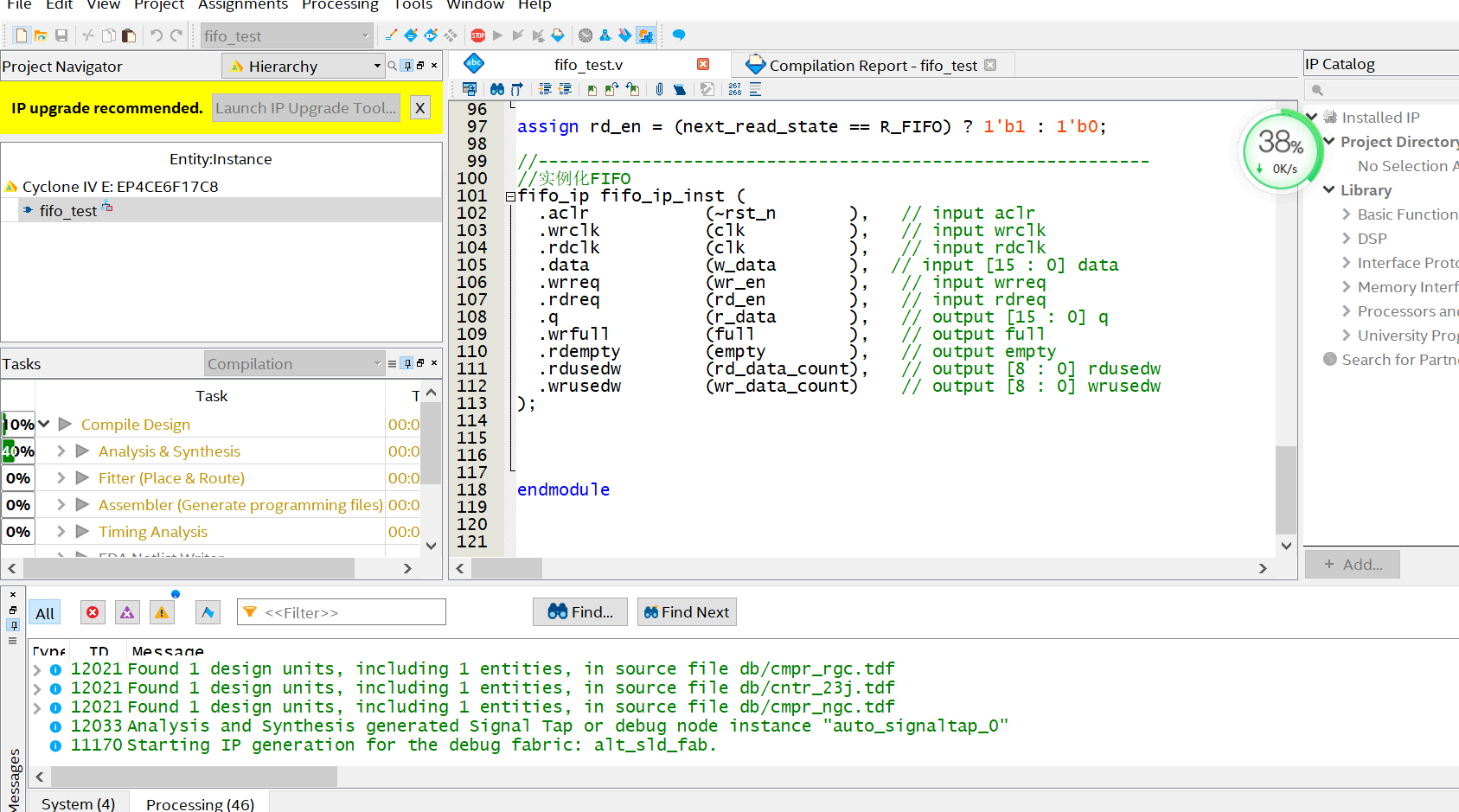

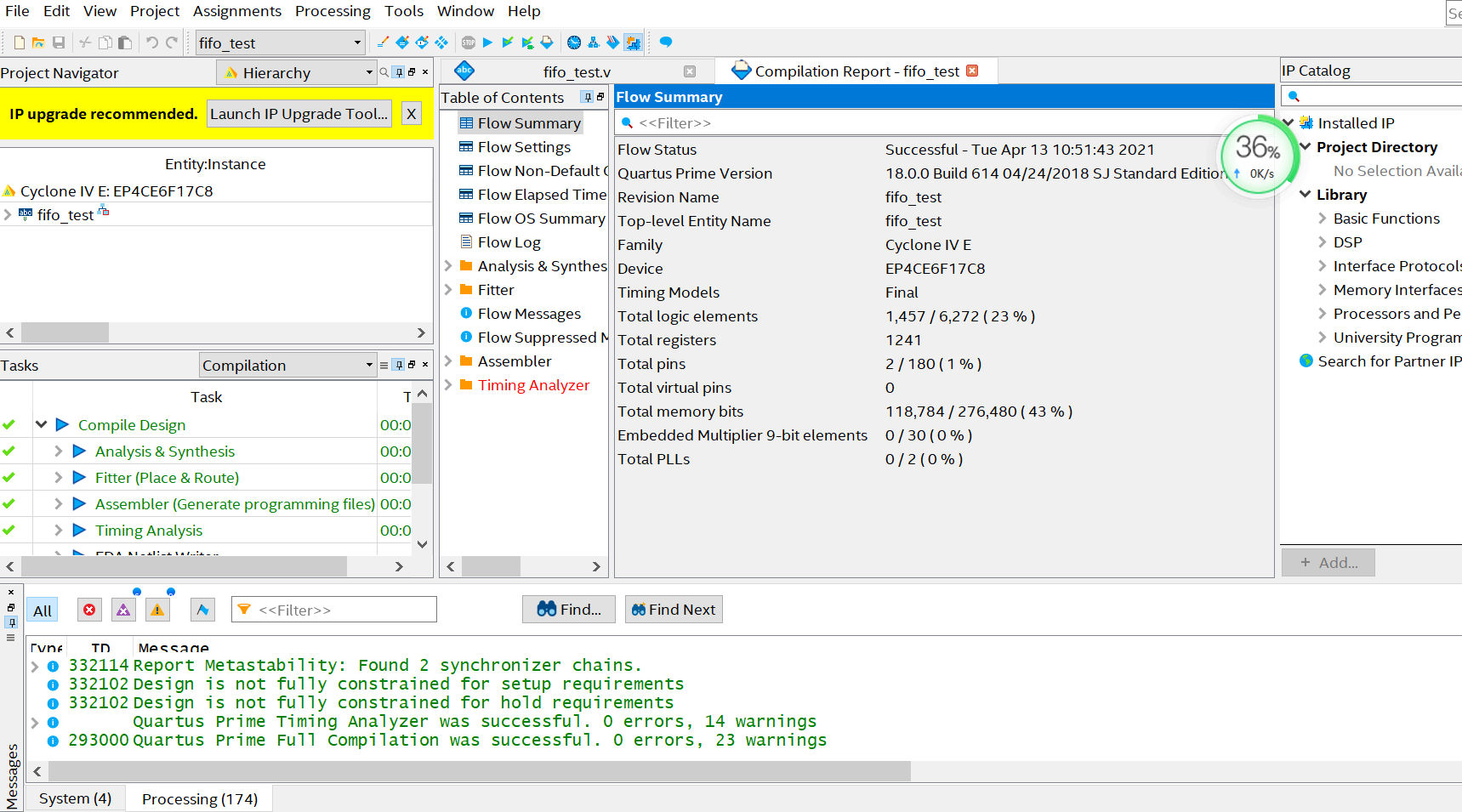

FPGA片内FIFO读写测试Verilog逻辑源码Quartus工程文件+文档说明,使用 FPGA 内部的 FIFO 以及程序对该 FIFO 的数据读写操作。FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

module fifo_test(

input clk, //50MHz时钟

input rst_n //复位信号,低电平有效

);

//-----------------------------------------------------------

localparam W_IDLE = 1;

localparam W_FIFO = 2;

localparam R_IDLE = 1;

localparam R_FIFO = 2;

reg[2:0] write_state;

reg[2:0] next_write_state;

reg[2:0] read_state;

reg[2:0] next_read_state;

reg[15:0] w_data; //FIFO写数据

wire wr_en; //FIFO写使能

wire rd_en; //FIFO读使能

wire[15:0] r_data; //FIFO读数据

wire full; //FIFO满信号

wire empty; //FIFO空信号

wire[8:0] rd_data_count;

wire[8:0] wr_data_count;

///产生FIFO写入的数据

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

write_state <= W_IDLE;

else

write_state <= next_write_state;

end

always@(*)

begin

case(write_state)

W_IDLE:

if(empty == 1'b1) //FIFO空, 开始写FIFO

next_write_state <= W_FIFO;

else

next_write_state <= W_IDLE;

W_FIFO:

if(full == 1'b1) //FIFO满

next_write_state <= W_IDLE;

else

next_write_state <= W_FIFO;

default:

next_write_state <= W_IDLE;

endcase

end

assign wr_en = (next_write_state == W_FIFO) ? 1'b1 : 1'b0;

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

w_data <= 16'd0;

else

if (wr_en == 1'b1)

w_data <= w_data + 1'b1;

else

w_data <= 16'd0;

end

///产生FIFO读的数据

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

read_state <= R_IDLE;

else

read_state <= next_read_state;

end

always@(*)

begin

case(read_state)

R_IDLE:

if(full == 1'b1) //FIFO满, 开始读FIFO

next_read_state <= R_FIFO;

else

next_read_state <= R_IDLE;

R_FIFO:

if(empty == 1'b1)

立即下载 FPGA片内FIFO读写测试Verilog逻辑源码Quart

下载说明与使用指南

下载说明

- 本资源需消耗 2积分

- 24小时内重复下载不扣分

- 支持断点续传功能

- 资源永久有效可用

使用说明

- 下载后使用解压软件解压

- 推荐使用 WinRAR 或 7-Zip

- 如有密码请查看资源说明

- 解压后即可正常使用

积分获取方式

- 上传优质资源获得积分

- 每日签到免费领取积分

- 邀请好友注册获得奖励

- 查看详情 →