资源详细信息

基于FPGA设计的字符VGA LCD显示实验Verilog逻辑源码Quartus工程文件+文档说明 - 资源详细说明

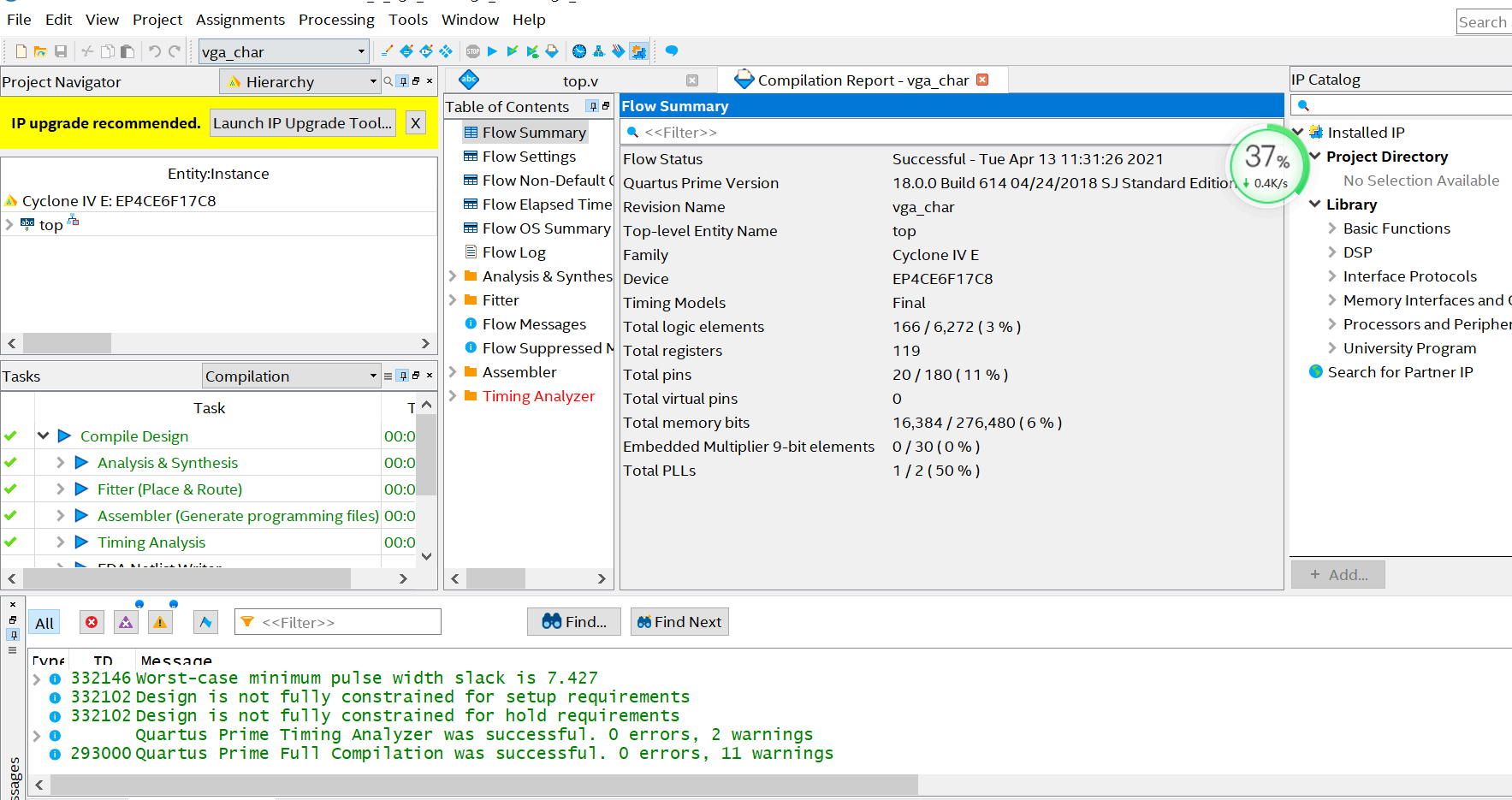

基于FPGA设计的字符VGA LCD显示实验Verilog逻辑源码Quartus工程文件+文档说明,通过字符转换工具将字符转换为 8 进制 mif 文件存放到单端口的 ROM IP 核中,再从

ROM 中把转换后的数据读取出来显示到 VGA 上,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

module top(

input clk,

input rst_n,

//vga output

output vga_out_hs, //vga horizontal synchronization

output vga_out_vs, //vga vertical synchronization

output[4:0] vga_out_r, //vga red

output[5:0] vga_out_g, //vga green

output[4:0] vga_out_b //vga blue

);

wire video_clk;

wire video_hs;

wire video_vs;

wire video_de;

wire[7:0] video_r;

wire[7:0] video_g;

wire[7:0] video_b;

wire osd_hs;

wire osd_vs;

wire osd_de;

wire[7:0] osd_r;

wire[7:0] osd_g;

wire[7:0] osd_b;

assign vga_out_hs = osd_hs;

assign vga_out_vs = osd_vs;

assign vga_out_r = osd_r[7:3]; //discard low bit data

assign vga_out_g = osd_g[7:2]; //discard low bit data

assign vga_out_b = osd_b[7:3]; //discard low bit data

//generate video pixel clock

video_pll video_pll_m0(

.inclk0 (clk ),

.c0 (video_clk )

);

color_bar color_bar_m0(

.clk (video_clk ),

.rst (~rst_n ),

.hs (video_hs ),

.vs (video_vs ),

.de (video_de ),

.rgb_r (video_r ),

.rgb_g (video_g ),

.rgb_b (video_b )

);

osd_display osd_display_m0(

.rst_n (rst_n ),

.pclk (video_clk ),

.i_hs (video_hs ),

.i_vs (video_vs ),

.i_de (video_de ),

.i_data ({video_r,video_g,video_b} ),

.o_hs (osd_hs ),

.o_vs (osd_vs ),

.o_de (osd_de ),

.o_data ({osd_r,osd_g,osd_b} )

);

endmodule

立即下载 基于FPGA设计的字符VGA LCD显示实验Verilog

下载说明与使用指南

下载说明

- 本资源需消耗 2积分

- 24小时内重复下载不扣分

- 支持断点续传功能

- 资源永久有效可用

使用说明

- 下载后使用解压软件解压

- 推荐使用 WinRAR 或 7-Zip

- 如有密码请查看资源说明

- 解压后即可正常使用

积分获取方式

- 上传优质资源获得积分

- 每日签到免费领取积分

- 邀请好友注册获得奖励

- 查看详情 →