提到3D芯片,更多的用户会想到3D打印机,或者3D电视,实际上,随着技术的进步,3D芯片早已面世,其特点在于可以利用更小的面积,布局更多的晶体管,以实现效率的提升和效能的降低。本文介绍了一种新技术,另3D芯片实现更低成本。

通常一提到3D晶片就会联想到采用矽穿孔(TSV)连接的晶片堆叠。但事实上,还有一些技术并未采用TSV,如BeSang公司最近授权给韩国海力士(SKHynix)的垂直晶体阵列技术。此外,由半导体研究联盟(SRC)赞助加州柏克莱大学最近开发出采用低温材料的新技术,宣称可带来一种低成本且灵活的3D晶片制造方法。

该技术直接在标准CMOS晶片上的金属薄层之间制造主动元件,从而免除了垂直堆叠电晶体或以TSV堆叠晶片的开销。

「对我来说,令人振奋的部份在于它是一款单晶片的整合,而不是采用至今在实现3D整合时所用的晶片堆叠技术,」SRC奈米制造科学总监BobHavemann表示,「这种方法能够以更低得多的成本提供更大的灵活性。」

利用金属顶层之间的主动元件,为晶片设计者提供一款有利的新工具。

「这种方式为设计领域带来了一个全新的境界──能够在任何金属层之间加进主动元件。设计者将为此新途径感到振奋,他们的梦想一直是能够随心所欲地在任何层加进主动元件,从而增加他们想要的功能与性能,现在他们的梦想得以成真。」

研究人员以低温材料制造低成本的3D IC

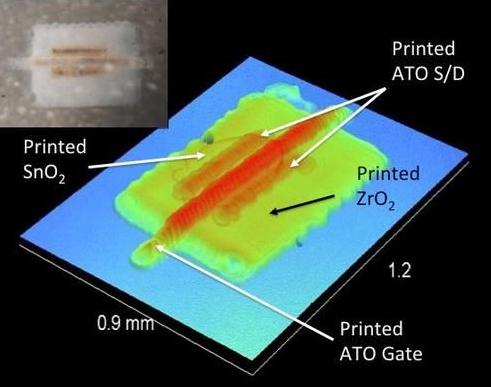

在CMOS基板上涂布氧化物(蓝色)的金属层上印制干涉式薄膜电晶体。

可以确定的是,能以够低的温度制造而又不至于干扰下层CMOS晶片层的电晶体在性能方面将会有所限制,但柏克莱大学的研究团队宣称,这些低温材料目前已经相当实用了,未来还会进展的更好。

「许多氧化物材料利用了工程师针对显示应用而开发的锡、铟、锌与镓,」加州大学柏克莱分校电子工程与电脑科学教授VivekSubramanian表示,「但它们所能达到性能数据够高,沈积温度够低,因而十分适合整合于CMOS金属层中。」

该技术的工作原理是先制造出CMOS晶片和第一层金属薄层。其后,设计者可自行选择在各金属层(目前的晶片最多达15层)之间添加更多主动元件,。

「事实证明,利用旋转涂层以及各种印制技术,你可以使用由该方案沉积而来的材料在CMOS金属层间制作出相当高性能的电晶体,」Subramanian说。

不过,这项制作电晶片的技术目前仍处于试验阶段,但其范围涵盖从旋转涂层以及用传统微影技术到制作图案,到以喷墨直接列印,或甚至是次微米级的凹印、奈米压印等其他技术。

「首先,我们在金属层表面增添一层电介质,然后在其上添加一层电晶体,」Subramanian说,「而最妙之处在于你可加进更多的电介质层,在各金属层之间任意交错电晶体。为此,你必需使用相容的材料,并在400℃(752℉)的温度下进行制造。我们目前已能沈积出氧化物与氮化物,并取得良好的性能了。」

可以确定的是,这些交错的电晶体还无法达到像CMOS上的矽晶电晶体一样的高性能,但在用于驱动感测器或存取记忆体等特定目的时,Subramanian表示使用这些交错的电晶体已经绰绰有余了。

「下一步我们打算利用透明导体在金属层上添加感测器,以便实现互连;此外,更有意义的是我们考虑用于3D晶片的许多材料与其他人打算用于‘电阻式随机存取记忆体’(RRAN)的材料是一样的,因而可能让我们在处堙上堆叠RRAM层。我们的下一步持续改善电晶体,以便能提供更多设计灵活度,然后再使其与RRAM、记忆体存取进行整合。」

SRC所赞助的这项开发计划属于一个三年计划中的第二年,接下来还将在SRC的半导体技术先进研究网路(STARnet)计划下展开进一步的研发,以期能在感测器、记忆体、显示器、封装与,可穿戴电子产品中找到更多新应用。