资源详细信息

电子书-RTL Design Style Guide for Verilog HDL540页 - 资源详细说明

电子书-RTL Design Style Guide for Verilog HDL540页

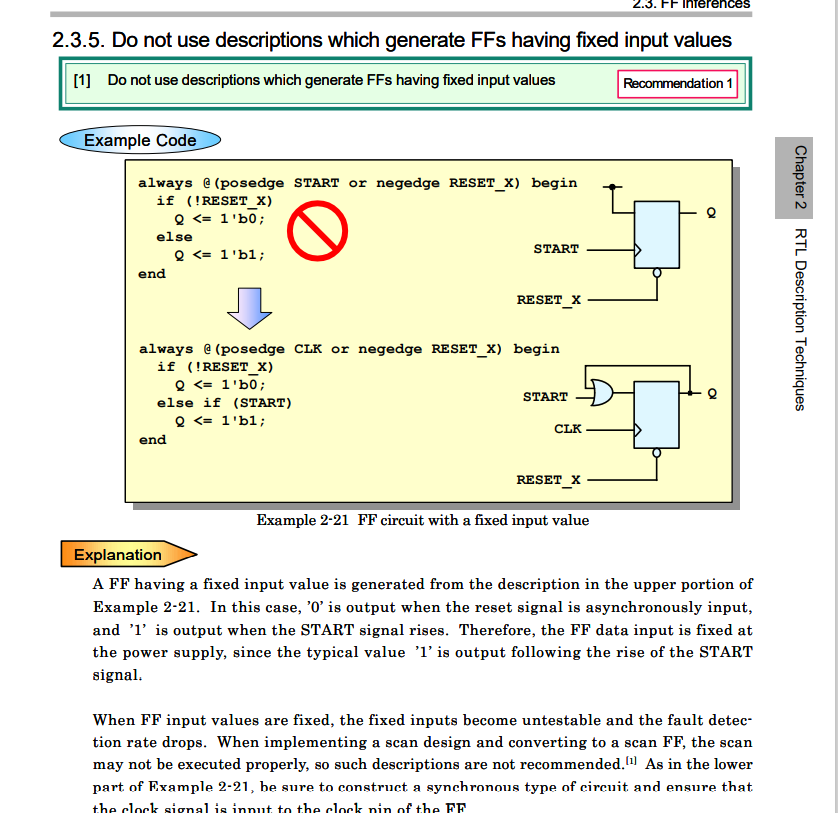

A FF having a fixed input value is generated from the description in the upper portion of Example 2-21. In this case, ’0’ is output when the reset signal is asynchronously input, and ’1’ is output when the START signal rises. Therefore, the FF data input is fixed at the power supply, since the typical value ’1’ is output following the rise of the START signal. When FF input values are fixed, the fixed inputs become untestable and the fault detection rate drops. When implementing a scan design and converting to a scan FF, the scan may not be executed properl not be executed properly, so such descriptions , so such descriptions are not are not recommended. recommended.[1] As in the lower part of Example 2-21, be sure to construct a synchronous type of circuit and ensure that the clock signal is input to the clock pin of the FF. Other than the sample shown in Example 2-21, there are situations where for certain control signals, those that had been switched due to the conditions of an external input will no longer need to be switched, leaving only a FF. If logic exists in a lower level and a fixed value is input from an upper level, the input value of the FF may also end up being fixed as the result of optimization with logic synthesis tools. In a situation like this, while perhaps difficult to completely eliminate, the problem should be avoided as much as possible.

立即下载 电子书-RTL Design Style Guide for

下载说明与使用指南

下载说明

- 本资源需消耗 2积分

- 24小时内重复下载不扣分

- 支持断点续传功能

- 资源永久有效可用

使用说明

- 下载后使用解压软件解压

- 推荐使用 WinRAR 或 7-Zip

- 如有密码请查看资源说明

- 解压后即可正常使用

积分获取方式

- 上传优质资源获得积分

- 每日签到免费领取积分

- 邀请好友注册获得奖励

- 查看详情 →