资源详细信息

Verilog HDl语言实现CPLD-EPC240与电脑的串口通讯QUARTUS逻辑工程源码 - 资源详细说明

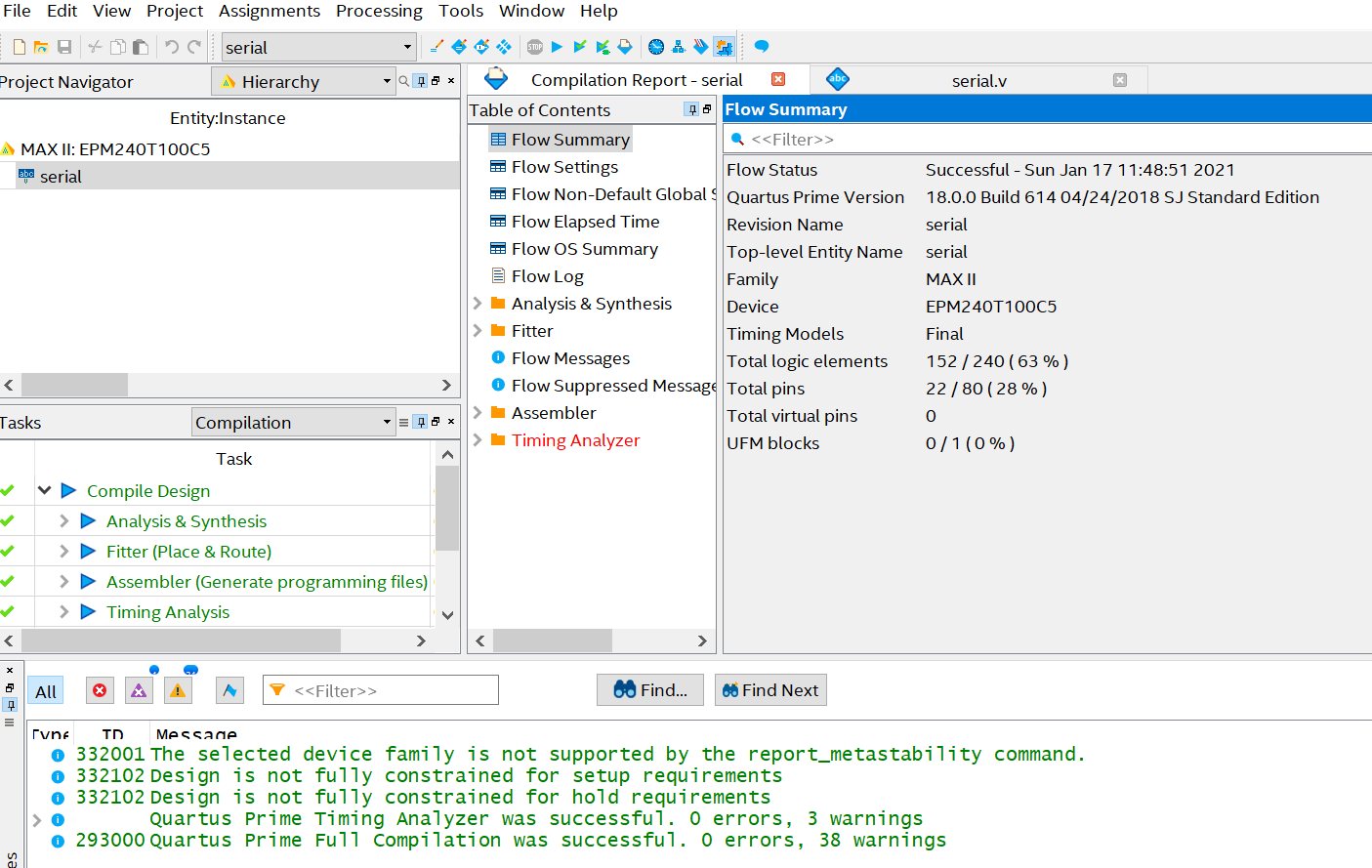

Verilog HDl语言实现CPLD-EPC240与电脑的串口通讯QUARTUS逻辑工程源码

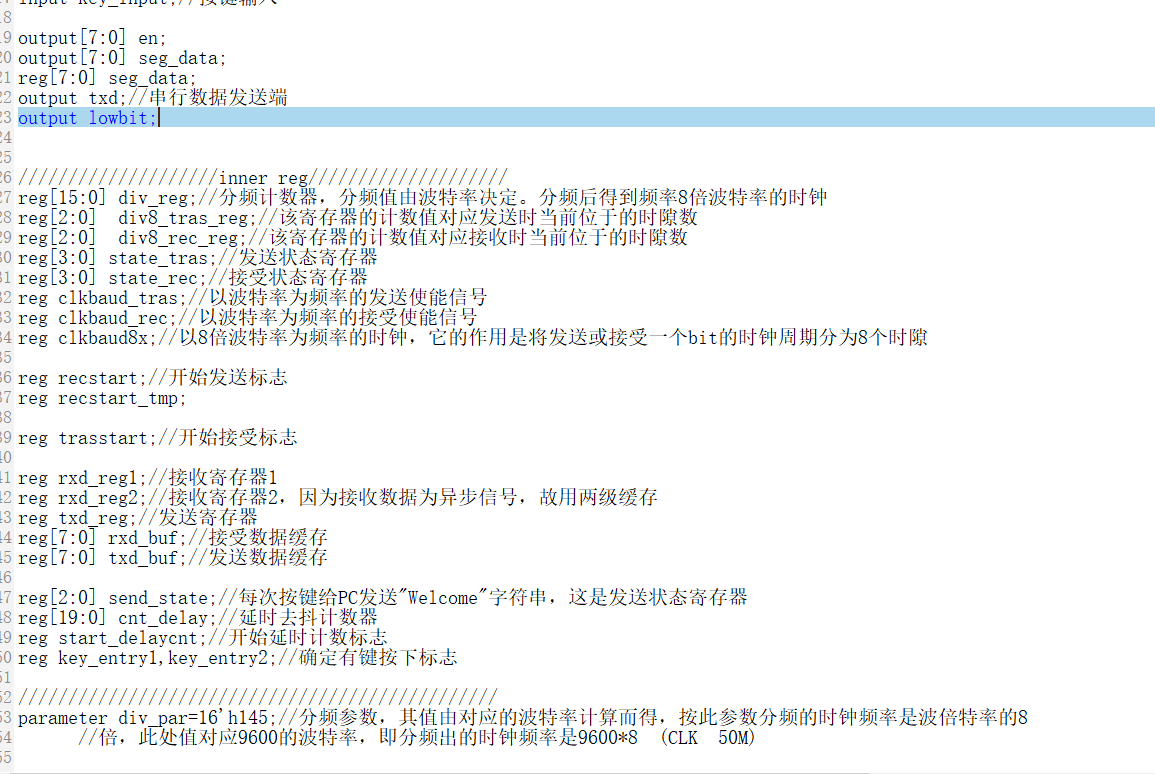

//本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在

//PC机上安装一个串口调试工具来验证程序的功能。

//程序实现了一个收发一帧10个bit(即无奇偶校验位)的串口控

//制器,10个bit是1位起始位,8个数据位,1个结束

//位。串口的波特律由程序中定义的div_par参数决定,更改该参数可以实

//现相应的波特率。程序当前设定的div_par 的值是0x145,对应的波特率是

//9600。用一个8倍波特率的时钟将发送或接受每一位bit的周期时间

//划分为8个时隙以使通信同步.

//程序的工作过程是:串口处于全双工工作状态,按动key1,FPGA/CPLD向PC发送“21 EDA"

//字符串(串口调试工具设成按ASCII码接受方式);PC可随时向FPGA/CPLD发送0-F的十六进制

立即下载 Verilog HDl语言实现CPLD-EPC240与电脑的

提示:下载后请用压缩软件解压,推荐使用 WinRAR 或 7-Zip

下载说明与使用指南

下载说明

- 本资源需消耗 2积分

- 24小时内重复下载不扣分

- 支持断点续传功能

- 资源永久有效可用

使用说明

- 下载后使用解压软件解压

- 推荐使用 WinRAR 或 7-Zip

- 如有密码请查看资源说明

- 解压后即可正常使用

积分获取方式

- 上传优质资源获得积分

- 每日签到免费领取积分

- 邀请好友注册获得奖励

- 查看详情 →